7 月 19 日消息,中国科学院微电子研究所今日发文,微电子所刘明院士团队提出了一种基于 TiN/ TiOxNy / TiOx / NbOx / Ru 结构的非细丝型自选通阻变存储器,并在 16 层三维垂直结构上实现。

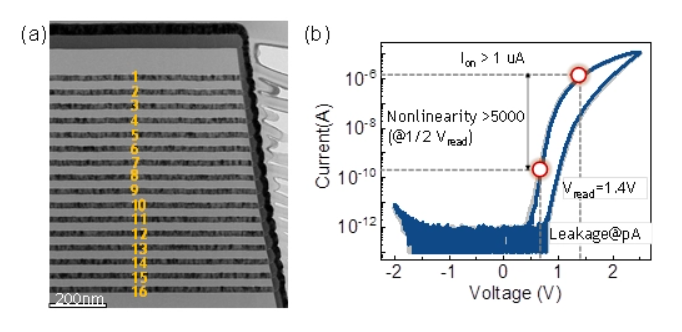

据介绍,该存储器实现了 50 倍开态电流密度的提升,并达到了高非线性(>5000)。TiOx 内部峰状势垒的形成有效提升了器件的非线性。第一性原理计算结果表明 Nb2O5 的氧空位聚合能为正值,这表明氧空位不容易发生聚集,器件可在较高电流下工作而不会发生击穿,从而实现高电流密度。

▲图(a)16 层三维垂直 RRAM 的 TEM 截面图、图(b)I-V 特性曲线

中国科学院微电子研究所表示,由于电流的提升,该器件的读延迟缩短至 18ns。该工作为实现具有高速、高密度的 3D VRRAM 提供了可能途径。

该成果以题为“16-layer 3D Vertical RRAM with Low Read Latency (18ns), High Nonlinearity (>5000) and Ultra-low Leakage Current (~pA) Self-Selective Cells”入选 2023 VLSI。微电子所博士生丁亚欣为第一作者,微电子所罗庆研究员和华中科技大学薛堪豪教授为通讯作者。